題組內容

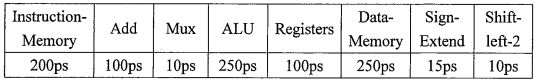

3. (8%) Assume that logic blocks needed to implement a processor's datapath have the following

latencies:

(a) (2%) Consider a datapath similar to the one in the textbook shown below, but for a processor

that only has one type of instruction: unconditional PC-relative branch. What would the cycle

time be for this datapath?