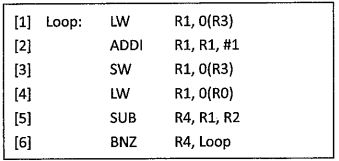

題組內容

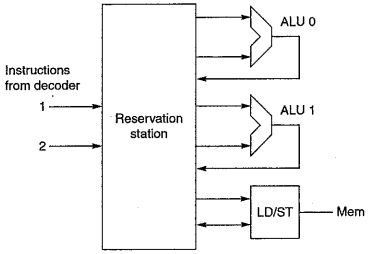

15. (5 points) Assume that we have the following machine instruction program. Also assume that our processor has the following microarchitecture that the arithmetic-logical units (ALUs) can do all arithmetic ops in the above program and that the Rcservation Station (RS) can simultaneously dispatch at most one operation to each functional unit per cycle (one op to each ALU plus one memory op to the LD/ST).

Also assume that our processor has the following microarchitecture that the arithmetic-logical units (ALUs) can do all arithmetic ops in the above program and that the Rcservation Station (RS) can simultaneously dispatch at most one operation to each functional unit per cycle (one op to each ALU plus one memory op to the LD/ST).

Suppose all of the instructions from the program in the above are present in the RS, with no renaming having been done.Please answer which of the following statements is/are correct ?Hint: An instruction with latency +2 requires two <stall> cycles to be inserted into the code sequence. Think of it this way: A one-cycle instruction has latency 1 + 0, meaning zero extra wait states. So, latency 1 + 1 implies one stall cycle; latency 1 + N has N extra stall cycles.)