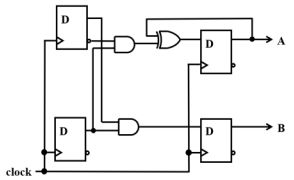

1 有一循序電路如下圖。依據晶圓代工廠所提供的元件庫(cell library) ,各元件的訊號延遲時間如下:AND gate 的延遲時間為 2 ns,XOR gate 的延遲時間為 4 ns,D flip flop 的 setup time 為 3 ns,clock-to-output time 為 1 ns。該電路能正確運作的最短時脈週期(clock period time)為何?

(A)6 ns

(B)8 ns

(C)10 ns

(D)12 ns

答案:登入後查看

統計: A(31), B(63), C(117), D(48), E(0) #2791017

統計: A(31), B(63), C(117), D(48), E(0) #2791017