題組內容

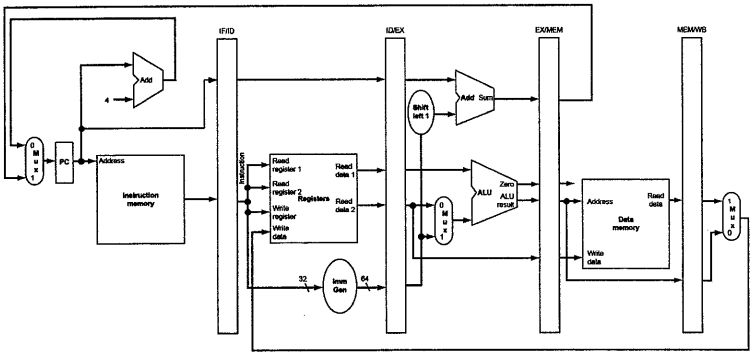

Please analyze the hazards in the assembly code which may cause the pipeline to stall, assuming all the instructions and data

are in the instruction and data caches and do not cause stalls in the IF and MEM stages.

Please analyze the hazards in the assembly code which may cause the pipeline to stall, assuming all the instructions and data

are in the instruction and data caches and do not cause stalls in the IF and MEM stages.