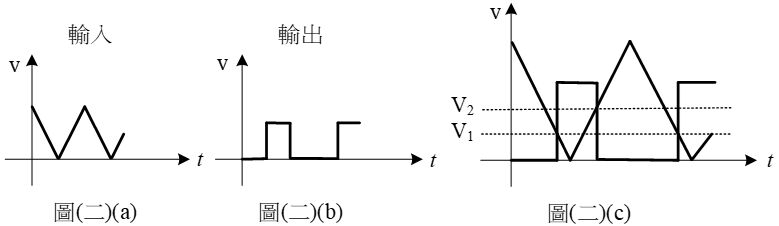

18. 有關邏輯準位的特性,一個 CMOS 反相器的雜訊邊限 ( Noise Margin ) 電壓之間的關係為 VIH > VIL、VOH > VOL,輸入與輸出信號如圖 ( 二 ) ( a ) 與 (b )所示,若將輸入與輸出波形 疊合如圖(二)( c )所示,則V1與V2的敘述下列何者正確?

(A) V1為VIH,邏輯閘的輸入高準位電壓

(B) V1為VIL,邏輯閘的輸入低準位電壓

(C) V2為VOH,邏輯閘的輸出低準位電壓

(D) V2為VOL,邏輯閘的輸出高準位電壓

答案:登入後查看

統計: A(4), B(19), C(9), D(1), E(0) #3433956

統計: A(4), B(19), C(9), D(1), E(0) #3433956