題組內容

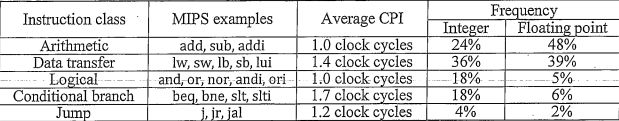

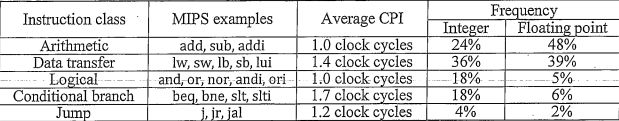

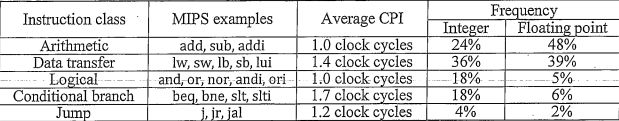

1. The following table shows the percentage of MIPS instructions executed by category for

average of SPEC2000 integer programs and SPEC2000 floating point programs.

1.3 Consider an architecture that is similar to MIPS except that it supports update addressing for

data transfer instructions. If we run SPEC2000int using this architecture, some percentage of the data

transfer instructions will be able to make use of the new instructions, and for each instruction

changed, one arithmetic instruction can be eliminated. If 25% of the data transfer instructions can be

changed, which will be faster for SPEC2000int, the modified MIPS architecture or the unmodified

architecture? How much faster? (Assume that both architectures have CPI values as given in the

above table and that the modified architecture has its cycle time increased by 20% in order to

accommodate the new instructions.)